2023-08-29

材料来源:雅时化合物半导体

系统设计人员现在可以从SiC MOSFET的新测试和应力程序中获益,该程序可以真实地确定其最坏情况下的阈值电压变化。

作者: Thomas Aichinger,英飞凌

与硅基同类产品相比,SiC功率MOSFET的最大优势之一是它能够在更高的开关频率和更低的损耗下工作。由于这一点,工程师可以建立先进的电力电子电路,这些电路具有更小的冷却单元和更小的无源元件。这些优势受到高度重视,不仅开辟了新的应用领域,而且使SiC MOSFET在现有的应用中取代了硅器件,为更轻、更高效的系统设计开辟了新天地。

当工程师们用SiC组件设计电路时,他们期望除了利用性能优势之外,与硅组件相比,他们不会因质量上的任何妥协而受到阻碍。这些工程师期望在使用寿命内具有可预测的电气参数稳定性。

不幸的是,直到最近,这些工程师最初的总体印象是,SiC技术还没有完全成熟。例如,有人担心迄今为止未知的阈值电压(VTH)的特性,以及在可靠性评估期间异常的电参数漂移。研究论文显示,在短时间应力下,VTH的变化很大,这使人们担心SiC MOSFET的关键电气参数是高度可变的,有可能在实际操作中迟早会失控。

直到最近,SiC MOSFET中这些短期VTH不稳定性的原因和应用相关性尚未完全了解,文献报道了广泛的参数变化。人们提出了各种可能的原因。一是第一代产品的质量水平参差不齐;第二个是一些基本问题阻碍了关键电参数(如阈值电压)的稳定、可重复测量。

最近,JEDEC发布了用于评估SiC MOSFET中V TH的新测量指南,解决了第二个问题,该指南是由英飞凌的团队贡献的。我们继续深入了解金属氧化物半导体(MOS)界面的俘获动力学。在本文的第一节中概述了这一点,它帮助我们调整了VTH测量程序,从而解决了未定义的不可重复测量的问题。

有了可重复和可靠的VTH测量程序,我们取得了进一步的进展,最终以标准化的方式量化了电应力对器件状况的影响。这对于消除围绕SiC MOSFET技术的整体稳定性和可控性的主要担心非常有价值。我们的发现包括揭示了神秘的短期VTH变化是完全可逆的,并且在每个切换周期中都会重复出现。请注意,这种效应在市场上所有SiC MOSFET中都存在,并且已经存在于原始器件中,这并不值得警惕:这是一种固有的器件特性,而不是可靠性关键的退化机制。

我们的下一个重要步骤是发现如何以最现实的方式对SiC器件施加应力,这样我们就可以在MOSFET被用于其预期寿命的应用中之后确定最坏情况下的VTH变化。从历史上看,用于硅功率MOSFET检查系统VTH变化的方法是将这些器件升温,并在恒定的正或负栅极偏置下进行静态应力测试。对于高温栅极偏压测试,人们倾向于选择高于使用条件的应力温度和偏压,以便在1000小时(典型)的鉴定测试中覆盖芯片的整个寿命。这种测试产生的结果一直被认为是最坏的情况。人们一直认为,一种常见的替代方案--越靠近应用,栅极开关应力测试——不那么关键,因为它可能会在两者之间产生一些补偿性漂移效应和恢复阶段。我们质疑这一假设,工作表明这些因素不适用于SiC MOSFET。本文的第二部分描述了这些发现,以及我们全新的应力程序。

阈值电压的特性

VTH的稳定和可重复测量是重要的。需要用它来定义原始器件的数据表,并且必须在应力实验中评估V TH的演变。在硅MOSFET中,这项任务很简单,不需要任何特别的预防措施。原始硅功率晶体管总是显示相同的VTH。

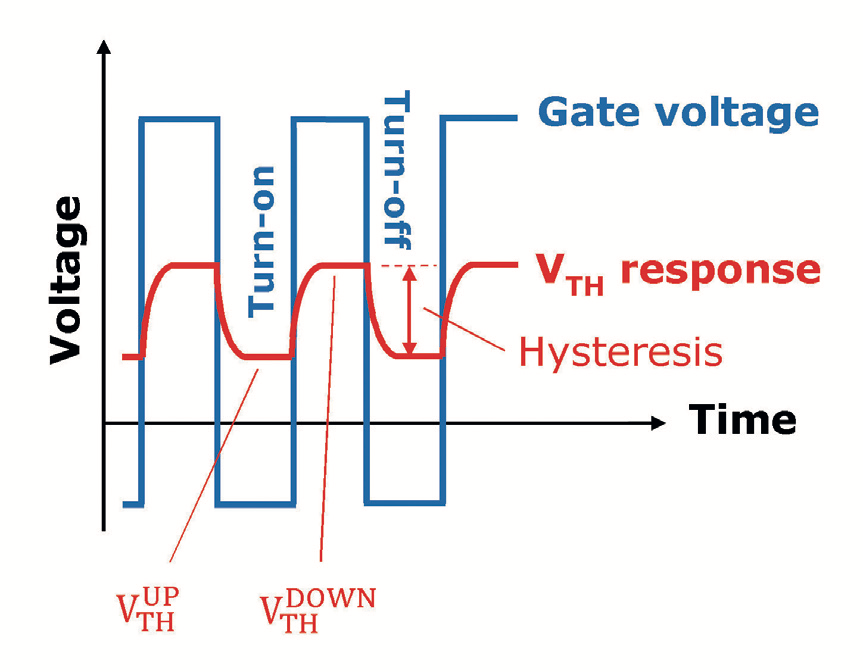

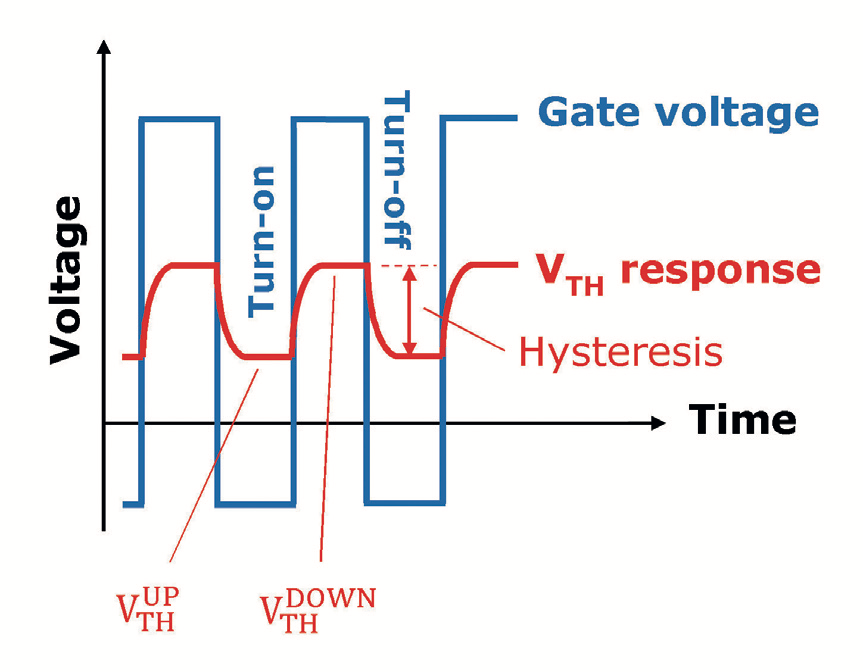

然而,在SiC MOSFET中情况并非如此,它的VTH不是恒定的。根据我们的测量,当晶体管导通时,来自负栅极电压的VTH显示不同的值;而当它关闭时,来自正栅极电压的VTH显示不同的值(见图1)。这表明需要定义VTH滞后:它是在接通期间的VTH,即所谓的上扫VTH(VTH UP), 和关断时的VTH,即所谓的下扫VTH(VTHDOWN)之间的差异。

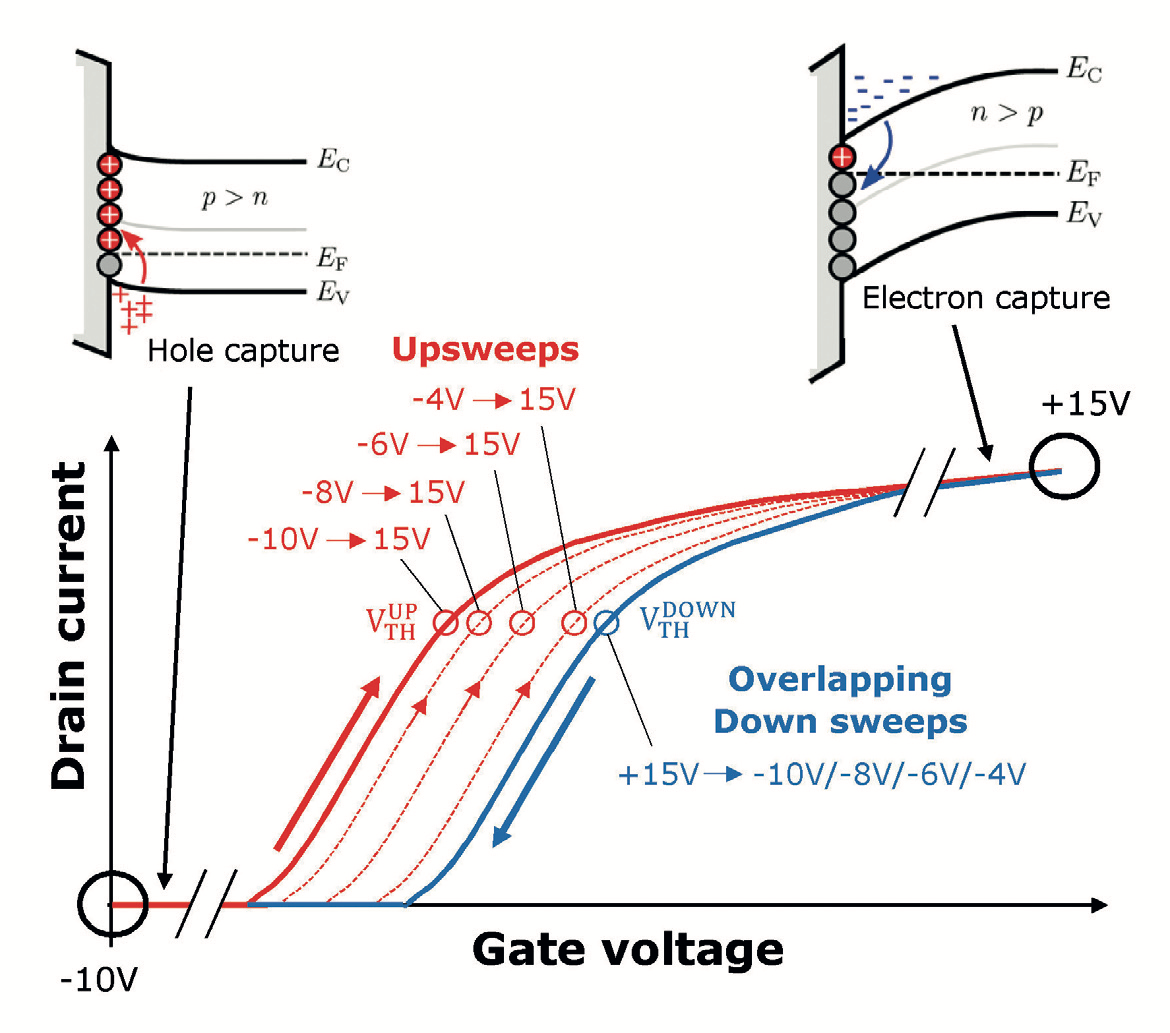

当栅极在深度累积和深度反转之间扫描栅极时,滞后是最大的,例如在-10 V和+15 V之间(这在图2中进行了说明,该图显示了SiC MOSFET在栅极电压快速上扫和下扫时的典型传输特性)。当上扫开始于接近0 V的电压时,以及当扫频较慢时,滞后现象会减少。

图1当以双极模式切换原始SiC MOSFET的栅极时,SiC MOSFET阈值电压动态图示。

图2 传输特性在开启和断开期间发生变化。由于在负栅极偏压下捕获的空穴,VTH在导通期间较低。在关断期间,由于在正栅极偏压下捕获电子,VTH更高。当上扫在接近0V的栅极电压水平处开始时,滞后减小,因为在负栅极电压期间捕获的空穴较少。

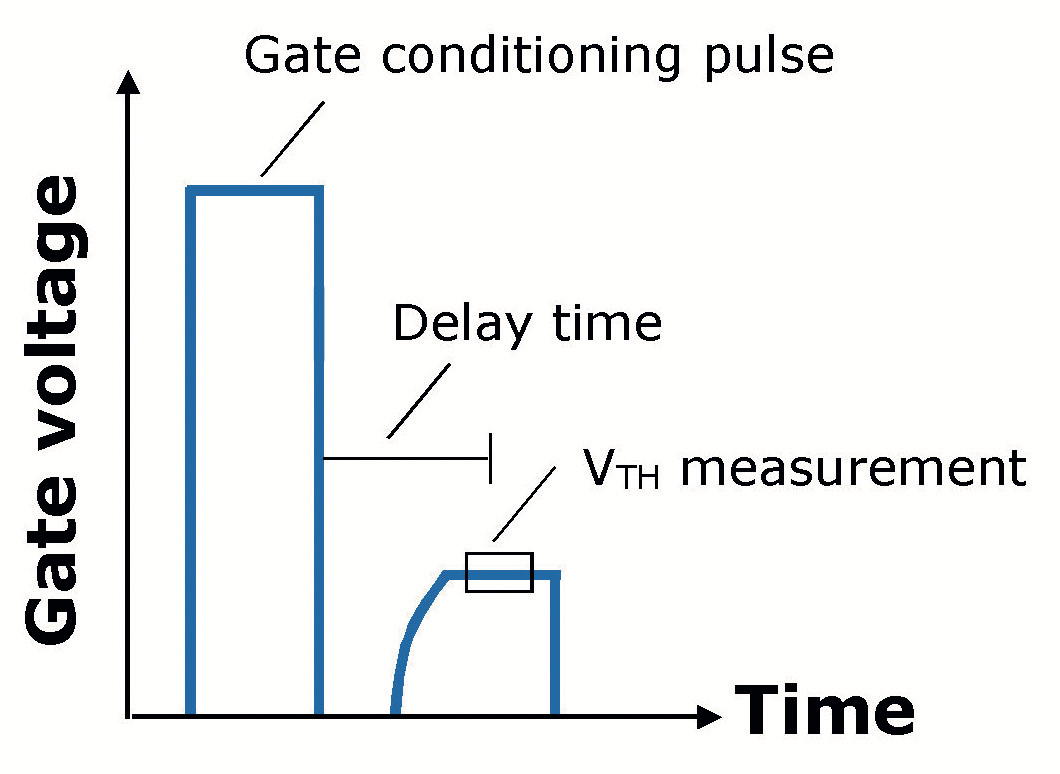

图3 栅极调节示例。在测量VTH之前,施加几毫秒的正栅极脉冲,以使MOS界面达到规定的充电状态。之后,使用例如门控二极管偏置方案执行VTH点测量。为了确保结果的再现性,调节脉冲和VTH测量之间必须有恒定的时间延迟。

图4 使用70 kHz和2 MHz之间的应力频率,在1011个开关周期之后,示例性阈值电压漂移。尽管总应力时间不同,但在相同数量的开关周期之后产生的VTH漂移实际上是相同的。

我们的研究表明,这些效应是由于位于靠近或直接位于SiC/栅极氧化物界面的预先存在的陷阱的短期充电和放电所致。我们已经确定,上扫的VTH总是较低的,因为由于从价带捕获的空穴,界面在栅极脉冲的负半周期中带正电荷。同时,下扫VTH总是更大,因为由于从导带捕获的电子,界面在栅极脉冲的正半周期中被中性充电,甚至被负充电。实际上,在磁滞包络内存在一个可能的VTH值的连续体,这是由于在几乎连续的缺陷带中捕获电荷的大量捕获和发射时间常数引起的。

这些发现的一个结果是,MOSFET的 "栅极偏置历史 "可以在很长一段时间内影响VTH测量。例如,当器件处于浮栅状态,或者在施加正或负的栅极脉冲后偏压在VGS = 0 V时,被困在中间间隙附近的电荷可能会在界面上 "储存 "数小时、数天甚至更长时间--这使器件处于非平衡状态。这是与SiC的大带隙相关的大的热发射势垒相关的。在硅MOSFET中没有类似的效应,因为它们具有较低的界面陷阱密度和较窄的带隙。

基于这些发现,我们知道用SiC MOSFET完成可重复的VTH测量的关键是首先要定义一个 "栅极偏置历史"。一种选择是对器件施加一个短的正栅极脉冲,使用介于推荐使用电压和数据表中的最大允许电压之间的栅极电压(见图3)。我们称这种技术为栅极调节。一旦进行, VTH必须在一个恒定的时间延迟下进行测量。

完成快速、适时的VTH点测量的一个简单方法是使用一个门控二极管测量方案。在这里,器件的栅极和漏极被短路,源极接地,并强制使用一个阈值电流,例如1 mA。最终,该栅极调节程序在SiC/栅极氧化物界面处创建了定义的、可再现的电荷状态,并实现了定义的,可再现的VTH测量。我们自己的研究与JEDEC最近发布的指南一致,表明更复杂的调节程序,包括负和正门调节脉冲,也允许重复测量滞后。

在以准确和可重复的方式跨越了测量VTH的障碍之后,我们承担了下一个挑战:通过开发用于确定不同应用的最坏情况VTH漂移的应力程序,控制和评估SiC MOSFET操作中的VTH不稳定性。

最坏情况下阈值电压漂移

质量是实现承诺的能力。因此,要在不同的应用和/或任务配置文件中实现SiC MOSFET的最高质量水平并确保其可靠运行,了解VTH和其他相关电气参数在使用寿命内的最坏情况变化至关重要。有了这样的洞察力,系统设计工程师可以考虑电气参数的潜在变化。

确定实际运行期间电气参数变化的最直接方法是运行完整的应用测试并测量器件在其规定使用寿命内的状况。 然而,这在大多数情况下是不现实的。 这是因为要得出一个最终的结果太耗时了,而且可能的应用种类太多,无法在单个持久的应用程序测试中进行检查。

为了在采用实际方法的同时确保质量管理,最佳做法是选择最坏情况下的应力条件,并努力简化应力程序,但不会改变相关的退化机制。这样做的好处之一是,一次应力测试涵盖了所有允许的应用条件。也可能有机会转向简化的应力程序,这可能为加速和并行化提供一些潜力。

另一种看待这个问题的方法是,理想的应力程序应该包含所有重要的应力源,以解决与特定应用相关的退化机制,但同时要避免不影响最终漂移结果的应用条件,或阻碍样本量的扩大和应力的加速。 为了发现这种统一的应力程序,我们发现研究不同SiC MOSFET应用的共同方面并确定主要的应力源是很有用的。

当SiC MOSFET被用于开关应用时,它们通常以5kHz至500kHz之间的频率运行。除了快速切换外,通常还需要宽而灵活的栅极驱动操作窗口,包括过冲、欠冲和负栅极关断电压的余量,以实现安全关断。因此,在SiC MOSFET的使用寿命中,它经常暴露于大量的双极栅极开关事件。

基于SiC MOSFET的典型特性,当该器件被部署在实际应用中时,以脉冲栅极模式而不是直流模式对其施加应力,以触发决定该晶体管中VTH不稳定性的相同退化机制,是非常合适的。我们团队以及在中国独立工作的学术研究人员最近的发现强调了这一点,即与静态栅应力相比,SiC MOSFET在双极栅开关条件下显示出不同甚至增强的参数不稳定性。这种机制被称为栅极开关不稳定性。

这项工作的另一个关键发现是,对于任何给定的栅极开关条件,所产生的阈值电压漂移主要取决于栅极开关事件的数量(见图4)。与我们的研究结果一致,中国的一个团队后来独立证实,总应力时间和占空比的频率并不重要,甚至不重要。根据这一发现,对于一个给定的应用情况,我们发现有可能通过简单地对器件施加应力到其最大的栅极开关周期数来确定VTH的时间演变。我们已经表明,这可以通过使用高达2MHz的高应力频率来加速完成。

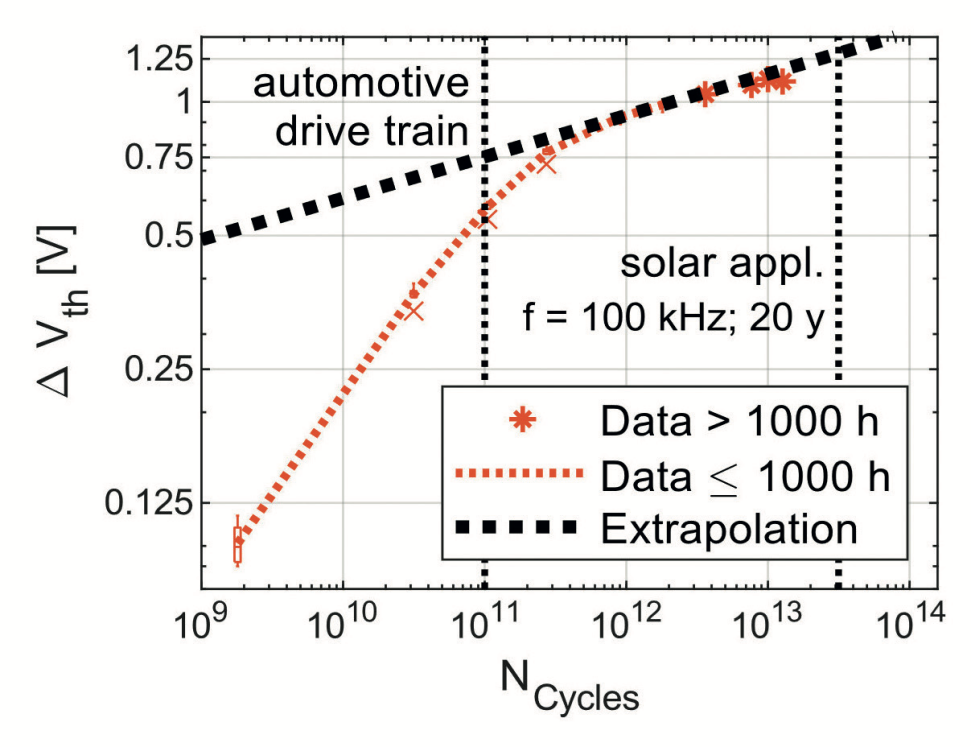

图5 由于栅极开关应力导致的最坏情况VTH漂移演化曲线示例。该测量是在最大数据表条件和500 kHz下进行的。粗虚线(黑色)表示饱和状态下数据点的幂律拟合,但在总应力时间1000小时内,对应于约2 x 1012个循环。在7000小时的应力时间(>1013个循环)内记录的其他数据点证实了幂律拟合的有效性。

为了涵盖所有可能的应用,必须使用数据表中允许的最关键工作条件,将器件施加最坏情况下的应力,这意味着使用VGS,max和VGS,min。采取这种方法也暴露了在应用中可能出现的栅极信号的过冲和欠冲,并影响栅极开关的不稳定性。

我们发现,不同制造商的器件在不同温度应力下的表现是不同的。一些SiC MOSFET在较低的温度下漂移较多,而另一些在较高的温度下漂移较多。由于这些变化,对于来自不同制造商的器件来说,哪种温度才是最坏的情况,这一点还很不明显。

通过合作,我们又测试了两个潜在的与应用相关的应力源:漏极电压和负载电流。这项研究表明,两者都没有导致VTH不稳定性的改变。这是一个极其有益的负面结果,因为它可以大大简化应力程序,而不会忽略实际应用中存在的任何重要的VTH应力源。

使用500 kHz的应力频率和栅极电压和温度的最大数据表条件,我们进行了测量,从而绘制出了示例性的VTH漂移演变曲线(见图5)。总的应力时间为7000小时,应力中断多次,使用前面描述的栅极调节方法记录VTH。对于较少的开关周期(<1011个周期),VTH漂移演化曲线的斜率更高,并且在超过1011–1012个开关周期时趋于饱和。

为了评估任意应用曲线结束时的最坏情况下的漂移,必须在内插或外推VTH漂移演变曲线之前,计算栅极切换事件的总数。该曲线也可用于计算其他相关电气参数的变化,如导通电阻。在这种情况下,值得注意的是,VTH的变化主要影响作为功率器件总导通电阻的组成部分的沟道电阻。电阻的其他组成部分,如与JFET、漂移区和衬底有关的部分,不受VTH不稳定性的影响。

在应用说明中,我们公司发布了与图5所示相似的参数漂移演变曲线。利用这些信息,我们的客户能够直接提取特定技术在特定应用中可预期的最大漂移。例如,对于汽车驱动应用,直到应用结束时的开关循环的总数相对较低,通常在1011周期左右。这使得最大的VTH漂移可以直接从原始数据中读取,如图5所示。

然而,对于太阳能应用,其特点是在20年或更长时间内,在通常70-100kHz的频率下运行,数据必须被推断出来,因为真正的应用结束曲线测试会导致不合理的长应力时间。用于这种幂律推断的曲线如图5所示。

简而言之,在我们努力提高对SiC/栅极氧化物界面的俘获动力学的理解的基础上,我们继续开发新的表征和应力程序,以适应SiC MOSFET的特性。

这些新方法提供了标准化的、可重复的测量,以及对实际应用中随时间变化的参数的现实评估。反过来,这使工程师能够预测器件特性在应用过程中会如何演变,并为SiC MOSFET达到其下一个卓越质量水平铺平道路。

拓展阅读

† T. Aichinger et al. “Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs” Microelectron. Reliab. 80 68 (2018)

† K. Puschkarsky et al. “Understanding BTI in SiC MOSFETs and Its Impact on Circuit Operation,” IEEE Trans. Device Mater. Reliab. 18 144 (2018)

† JAP183, “Guidelines for measuring the threshold voltage (VT) of SiC MOSFETs”, www.jedec.org

† JAP184, “Guideline for Evaluating Bias Temperature Instability of Silicon Carbide Metal-Oxide-Semiconductor Devices for Power Electronic Conversion”, www.jedec.org

† P. Salmen et al. “A new test procedure to realistically estimate end-of-life electrical parameter stability of SiC MOSFETs in switching operation”, IEEE International Reliability Physics Symposium (IRPS) (2021)

† H. Jiang et al. “Dynamic gate stress induced threshold voltage drift of silicon carbide MOSFET”, IEEE Electron Dev. Lett. 41 1284 (2020)

† X. Zhong et al. “Bias Temperature Instability of Silicon Carbide Power MOSFET Under AC Gate Stresses,” IEEE Trans. Power Electron. 37 1998 (2022)

† M.W. Feil et al. “On the Frequency Dependence of the Gate Switching Instability in Silicon Carbide MOSFETs”, Proceedings ICSCRM, Davos, 2022

† M. Sievers et al, “Monitoring of parameter stability of SiC MOSFETs in real application tests”, Microelectron. Reliab. 114 113731 (2020)

† Infineon Application Note 2018-09

扫一扫,在手机端打开当前页

- 上一篇:反向极化为绿光LED注入活力

- 下一篇: 化合物半导体的自动单晶圆灰化