2023-09-19

材料来源:雅时化合物半导体

作者:袁俊,王宽,郭飞,徐少东,成志杰,陈伟,吴阳阳,彭若诗,朱厉阳,李明哲

功率半导体器件是电力电子装置中电能转换 与电路控制的核心元器件,随着近年来新 能源汽车、光伏、轨道交通、智能电网等产业的 发展,市场对功率器件的需求迅速升温。然而,传统的体硅或SOI 基电力电子设备受限于自身材料结构和特性,在电能转换效率、重量和体积方面越来越显示出不足和局限性,难以适应未来电力电子系统对“高效、绿色、低碳”功率半导体 器件的要求。相比之下,第三代半导体SiC材料在禁带宽度、导热性能、临界击穿场强、电子饱 和漂移速度上的优势明显,符合未来电力电子系统小型轻量化、高效一体化、安全可靠化的发展趋势。同时SiC 功率器件产业具有巨大的经济效益,处在一个快速发展的市场中,随着全球“碳达峰、碳中和”目标的逐步实现,预计未来车规级SiC器件年复合增长率将超30%,SiC功率器件的市场规模可达万亿。

SiC 功率器件的研究从上世纪80 年代开始,目前SiC 二极管和MOSFET 晶体管应用最广泛、产业化成熟度最高,SiC IGBT 和GTO 等器件由于技术难度更大,仍处于研发阶段,距离产业化有较大的差距。而随着SiC 功率器件的演进,沟槽结构成为二极管与MOSFET 器件的主流设计,沟槽结构的优势有:(1)SiC 沟槽二极管可以构建更深的P 型掩蔽,大大减小了反向阻断时结位置的电场强度,从而降低二极管的漏电流,提高了器件的热稳定性;(2)SiC沟槽MOSFET将导电沟道从水平的晶面转移到了表面电子迁移率更高的竖直晶面,并消除了JFET 区域,使器件的导通电阻更低,减小了导通损耗,因此SiC 沟槽MOSFET具有更高的单元密度,极低的寄生电感,以及更快的开关速度。国外对于SiC 沟槽器件的研究较早,二极管与MOSFET 均已有产品上市,而国内对SiC 平面器件的技术研究较多,在沟槽器件的研究上处于起步阶段。以SiC MOSFET 为例,日本Rohm 和德国Infineon 在2015 年至2016 年推出了第三代沟槽MOSFET 器件,并逐渐形成专利壁垒;Rohm 在2021 年推出了业界最先进的第四代沟槽MOSFET 器件,并同步开始第五代沟槽技术的研发。而国内2014 年才开始第一代和第二代平面MOSFET 的研发,目前刚实现小批量应用。在第三代沟槽MOSFET 方面面临日美和欧洲的专利封锁,并且在第四代与第五代沟槽MOSFET 器件IP、结构设计与全套工艺环节存在很大的差距。

九峰山实验室聚焦于下一代SiC 沟槽器件领域的研究,集中资源开发了SiC 沟槽器件制备中的沟槽刻蚀、高温栅氧、离子注入等关键核心单点工艺,形成了自主可控的成套工艺技术。接下来,本文将围绕下一代SiC 沟槽器件技术,介绍业界在二极管及MOSFET 器件上的相关研究进展与阶段性成果。

碳化硅多级沟槽二极管技术

SiC 肖特基二极管(SBD)在导通时只有多数载流子参与导电,而PIN 二极管在导通时有少数载流子的注入,因此SBD 具有更高的关断速度以及更低的开关损耗,这也是SiC SBD 受到更广泛应用的主要原因。当工作在反向阻断状态时,SBD 主要通过金属与SiC 漂移区形成的肖特基结来承压,肖特基结表面电场强度可以达到1.5~2.2MV/cm,在强电场作用下镜像力及隧穿效应会导致结势垒的下降,而反向漏电流与势垒高度呈指数关系,因此SBD 结处的强电场会给器件带来较大的反向漏电流,一方面会带来更多的关态损耗,另一方面也会降低器件可靠性。

如图1所示,为了解决SBD 反向漏电流较大的问题,2002 年Wolfspeed 发布了第一款SiC JBS 产品(结势垒肖特基二极管),通过在漂移区表面位置间隔注入P 区,来降低器件在反向承压时肖特基结处的电场强度,从而大大降低了器件的漏电流,同时实现了更高的击穿电压。但JBS 结构也在器件正向导通时引入了JFET 区,使得器件的导通电阻增加。2006 年Infineon 发布了第一款SiC MPS 产品(混合式PIN- 肖特基二极管)[1],MPS 器件结构与JBS 相似,相对于JBS 侧重于提高器件反向特性, MPS 更侧重于改善器件的正向特性,其设计目标在于引进PN结的电导调制作用降低SBD在高密度正向电流下的压降。为了进一步降低肖特基结处的电场,ROHM 在2016 年发布了沟槽型JBS[2],通过刻蚀沟槽后再离子注入,得到了更深的P 型掩蔽区,使得器件的反向漏电流进一步降低,但同时也在导通时带来了更加严重的JFET 效应。

图1:SiC二极管技术发展路线。

为了有效缓解SBD 反向漏电流(深P 掩蔽)与正向导通电阻(P 区JFET 电阻)之间的矛盾,九峰山实验室在2021 年设计了SiC 多级沟槽JBS/MPS[3]。如图2(a)所示, 通过在金属/ 半导体接触界面设计多级台阶沟槽,可以使得P 型离子沿沟槽方向注入更深,构造更好的电场屏蔽,从而抑制肖特基结势垒降低效应,减小了来自肖特基热发射及场发射的漏电流。与相同深度的单级沟槽器件相比,避免了因为SiC 中P 型离子注入深度有限而导致的深沟槽漏电问题。由仿真分析可知,深P 掩蔽层显著降低了多级沟槽JBS 的表面电场,对于结间距从1 到3μm 不等的4H-SiC 多级沟槽JBS 二极管,表面电场仅为0.18–0.95 MV/cm。因此,与相同离子注入条件下的传统平面JBS 结构相比,多级沟槽JBS 的反向泄漏电流可以减少2 个数量级。并且由于多级沟槽底部宽度更小,形成的JFET 区面积较小,减小了对二极管正向导通电阻的影响,多级沟槽JBS 在进一步增强SBD 器件耐压能力的同时还使得器件可以保持较低的正向导通电阻。

图2:SiC多级沟槽JBS结构示意图及电场仿真:(a)多级沟槽JBS结构示意图;(b)多级沟槽JBS反向承压电场的TCAD仿真结果;(c)多级沟槽JBS与传统JBS表面电场分布的对比。

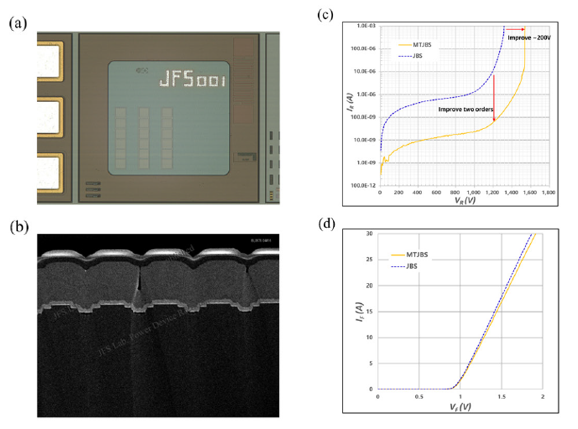

为了实现上述设计,九峰山实验室经过长期的工艺探索,成功刻蚀出SiC 多级沟槽结构,进行了沟槽角落的圆化,可以有效缓解槽角的电场集中效应,并开发出SiC 多级沟槽JBS 原型器件,实现了产品级技术的战略储备。如图3 所示,该1200V/20A 多级沟槽JBS 器件与相同工艺制备的平面JBS 器件相比,反向漏电流降低了2 个数量级,击穿电压增加了约200V,同时正向导通电阻没有明显增加。测试结果表明,所开发的多级沟槽JBS 器件在常温下施加1200V 反向电压时的反向漏电流低于60nA,超越业界现有的技术参数(CREE 典型值35μA),因其优越的电场屏蔽效果,在175℃及以上的高温环境下漏电流也仅为μA 级别,非常适合应用于电动汽车或高温恶劣环境的工控系统的功率模块。

图3:SiC多级沟槽JBS流片及电性测试结果:(a)多级沟槽JBS芯片的光学显微镜观测图;(b)芯片的SEM切片分析结果;多级沟槽JBS与传统JBS的(c)反向特性I-V曲线对比;(d)正向特性I-V曲线对比。

碳化硅沟槽MOSFET 技术

平面型SiC MOSFET 经过行业内多年的研究,现代技术进步已经达到了缩小MOS 元胞尺寸而无法降低导通电阻的程度,主要原因是由于平面MOSFET 的沟道迁移率差及JFET 颈区电阻的限制,即使采用更小的光刻尺寸,单位面积导通电阻也难以降到2mΩ · cm2,而沟槽结构可以有效解决这两个问题,其使导电沟道从横向变为纵向,相比平面结构沟道迁移率提升同时消除了JFET 颈电阻,大大增加了原胞密度,提高了功率半导体的电流处理能力。

然而,SiC 沟槽MOSFET 在实际工艺制作和应用中仍然存在几个问题:1.SiC 漂移区的高电场导致栅氧化层上的电场很高,这个问题在槽角处加剧,从而在高漏极电压下造成栅氧化层迅速击穿,同时对于恶劣环境的静电效应以及电路中的高压尖峰耐受能力差;2. 由于SiC 功率MOSFET 主要应用在高压高频大电流领域,电路中的寄生参数会使得在高频开关过程中产生overshoot 等尖峰毛刺,造成器件电流通路上的瞬时过压同时增加了开关过程的损耗;或由于功率负载等变化形成大的浪涌电压,因为现有沟槽MOSFET 器件本身并不具备抗浪涌电压自抑制能力和过压保护能力,往往需要在实际应用中设计复杂的缓冲电路,浪涌电压抑制电路和过压保护电路,而这种外部匹配的抑制和过压保护电路有时间上的延迟,实际开关过程中的高频尖峰电压浪涌仍然由器件本身承受,有时会导致器件沟道区的击穿失效,以及栅结构和电极欧姆接触区域的逐渐失效,引起器件可靠性问题;3. 离子注入深度有限,导致很多针对性的沟槽栅极保护结构和抗浪涌设计从工艺上难以实现。

为了更好的保护沟槽MOSFET 的栅极氧化层,特别是底部和沟槽角落,以及获得更好的抗浪涌和短路耐受能力, 业界目前仅有两种规模量产的SiC 沟槽MOSFET 专利结构, 其中日本Rohm 采用在栅极沟槽两侧构造源极双沟槽结构屏蔽中间的栅极沟槽底部,德国Infineon 采用“P+ 半包裹的非对称沟槽结构”。国内对于沟槽MOSFET 的研究才刚刚起步,在沟槽MOSFET 的器件IP、结构设计与核心工艺环节同国际水平存在很大的差距,并且面临日美欧的专利封锁。因此,沟槽MOSFET 成套工艺及结构IP,是未来十年碳化硅Fab 竞争的入场券。

九峰山实验室前瞻性地完成了沟槽MOSFET 的专利布局,成为国内具有完全自主沟槽结构的单位,避免了未来的专利纠纷。目前针对沟槽MOSFET 元胞结构、终端设计等领域已经获得多篇授权专利,包括“胶囊沟槽”系列,“包角沟槽”系列,“双侧导通半包沟槽”系列等,并在进一步完善相关技术的专利布局。

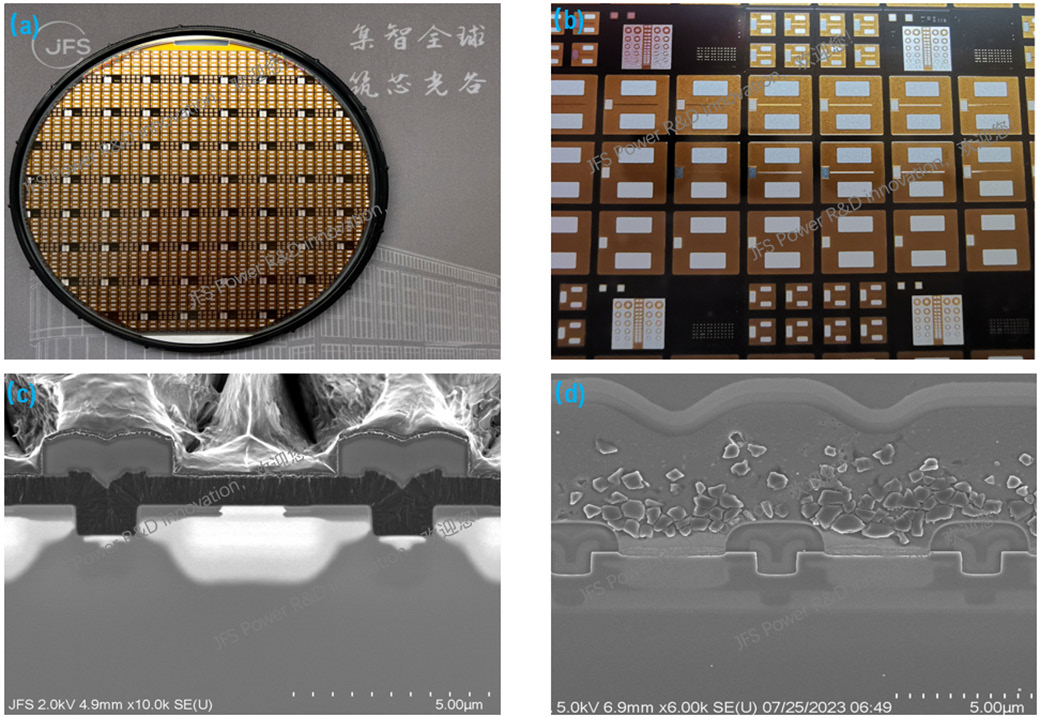

如图4 所示,为九峰山实验室的“胶囊沟槽”结构。该方案在栅极沟槽的两侧设计了P+ 掩蔽结构,P+ 掩蔽结构可以是直接离子注入形成的,也可以是先形成源极辅助沟槽再离子注入,增加离子注入的深度,当源极辅助沟槽为多级沟槽时,无需高能量高剂量的离子注入即可实现更深的P+ 掩蔽;并且通过二次外延的方法在n- 漂移层中形成P+ 埋层来达到电场屏蔽的效果,同时在栅极沟槽底部设计p-shield 来进一步保护沟槽底部及拐角位置的栅氧,p-shield 通过周期性的与P+ 埋层连接来实现接地效果。上述三种结构共同降低了栅氧中的电场强度,解决了电场集中区域容易出现击穿的问题,提高了器件对恶劣环境的静电承受能力以及对电路中高压尖峰的耐受能力。通过向栅极沟槽下方的P+ 埋层注入n 型离子形成N-Enrich 区域的方式来形成导电通路,从而自然在器件的漏极电流通路上引入了JFET 结构,且JFET 结构的导通特性可以由N-Enrich 区域的图形设计和离子注入浓度及图形轮廓进行优化调整,设计和工艺灵活, 具有较好的可制造性。此JFET 结构通过源极的P+ 掩蔽结构接地,在大的浪涌电压下可以自动扩展两侧的耗尽区从而增大JFET 区的导通电阻,相当于一个缓冲器电路结构自行抑制浪涌尖峰。同时在浪涌电压过大时,两侧耗尽区域继续扩展而相互重叠,起到封锁效应,保护内部的沟槽栅氧,起到一定的尖峰电压过压保护作用。虽然在引入JFET 后会增加一定的导通电阻,却具有了开关缓冲和浪涌电压自抑制效果,能增加器件对于浪涌电压和过电压的自抑制抗性,避免过压保护电路和过流保护电路由于实际作用上的时延造成的器件损坏和可靠性的减损。而且还可以对电路开关过程中的尖峰起到缓冲作用,减小开关损耗,可以减少电路设计中的缓冲电路/缓冲器电路结构,减少离散性的元器件,从而降低成本,也减少了实际模块体积,增强SiC 模块的可靠性。

图4:SiC“胶囊”沟槽MOSFET结构示意图。

图5:SiC“胶囊”沟槽MOSFET DEMO晶圆及器件SEM结构。

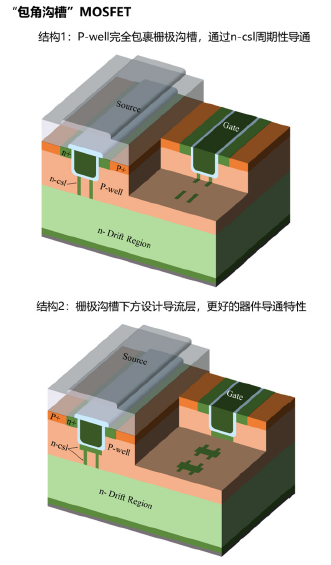

如图6 所示,为九峰山实验室的“包角沟槽”结构。该方案通过构造比栅极沟槽更深的P 阱区,使P 阱区包住槽角,通过沟槽底部的两条柱状N 型离子注入区形成导电通道。导电通道在沿沟槽方向是间断排布的,使得导电通道中间的P 型区域可以通过与P 阱区互联从而接地。在“包角沟槽”MOSFET 中,比沟槽更深、包裹住槽角的P 阱区可以有效降低槽角处的电场,防止槽角电场集中处栅氧的击穿,增强了器件的可靠性。同时通过精确的掺杂浓度设计, 当器件工作在反向阻断状态时,沟槽下方的N 型导电通道区和P 阱之间会相互耗尽、达到半超结效果,在提高器件击穿电压的同时也可以降低器件的导通电阻。在器件实际制备时,P 阱区可以通过二次外延形成,避免了对产能影响严重的SiC 高温高能Al 离子注入工艺,N 型导电通道区在栅极沟槽刻蚀完成后通过离子注入形成,整体方案在提升SiC 沟槽MOSFET 性能的同时,还兼顾对fab 厂制备产能的提升。

图6:SiC“包角”沟槽MOSFET结构示意图。

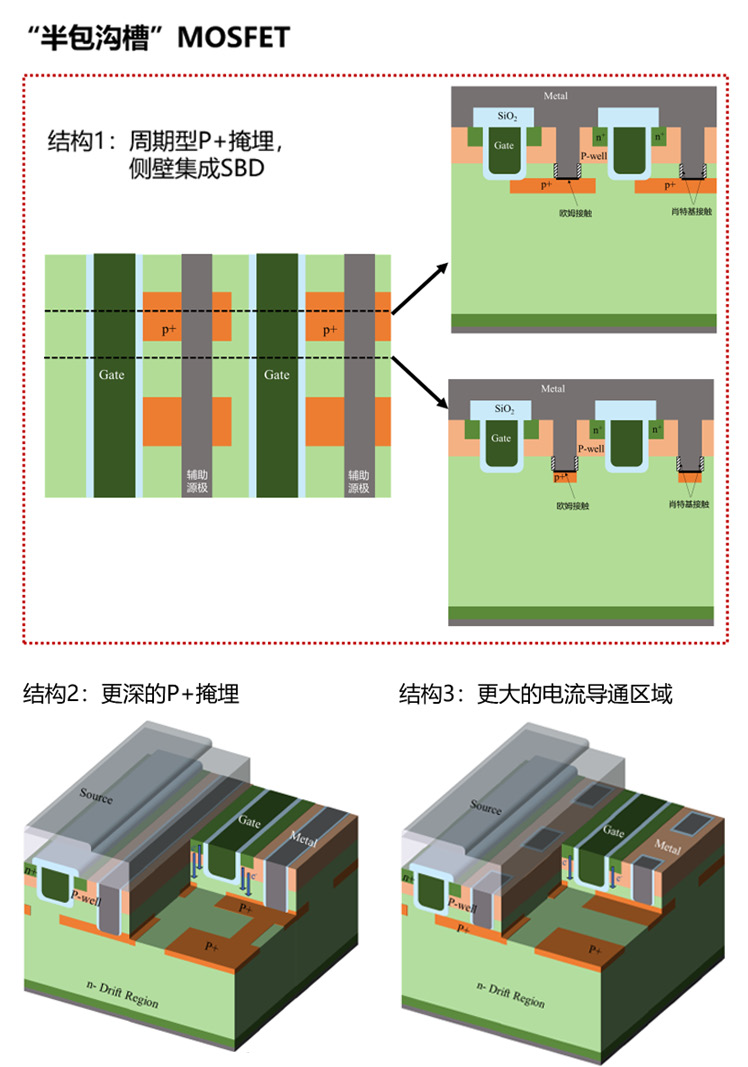

如图7 所示,为九峰山实验室的“半包沟槽”结构。在实际器件制作及产品应用中,Infineon 的非对称沟槽MOSFET 呈现了更好的沟槽栅底部保护能力和可靠性。从器件结构分析和TCAD 仿真上,也能体现出采用底部及沟槽一侧P+ 半包裹保护的方式能构造更好的沟槽栅电场屏蔽,然而,采用Infineon 的“半包沟槽”结构会造成沟槽MOSFET 只能通过一侧沟道来导电,另一侧被用来构造P+ 屏蔽层从而牺牲了导电沟道,造成器件单元导通损耗的增加。九峰山实验室的双侧导通“半包沟槽”结构采用一侧构造辅助源极沟槽二极管,同时结合沟槽栅底部P+ 掩埋层的方式, 使得栅极沟槽两侧的沟道都可以进行电子的输运,构造更好的双侧导通能力的“半包沟槽”MOSFET,增加器件的导通能力。P+ 掩埋层通过辅助源极沟槽接地,并且在与栅极沟槽平行方向上非连续,在空间上呈周期性分布,当栅极沟槽底部没有P+ 掩埋层时栅极两侧沟道都可以导通。这样也使得器件中P+ 掩埋层的layout 版图设计更加灵活,能结合具体需求来设计掩埋P+ 的面积占比,灵活调节导通电阻与抗浪涌及短路能力。同时,可以在辅助源极沟槽的侧壁集成肖特基二极管,底部形成欧姆接触,巧妙的将肖特基二极管集成到沟槽MOSFET 中,形成更好的续流特性。3D 仿真结果表明,优化后的双侧导通“半包沟槽”MOSFET 相对于Infineon 的CoolSiC 沟槽MOSFET,槽角栅氧最大场强降低2.8%,比导通电阻降低30.9%,Baliga 优值提升36.6%,在提升器件可靠性的同时大大降低了器件的导通损耗,达到了业界的先进水平。

图7:SiC“半包”沟槽MOSFET结构示意图。

碳化硅超结技术

SiC 功率器件优化的重要目标是减小各击穿电压(BV) 等级下器件的比导通电阻(Ron,sp), 即持续提升器件的Biliga 优值(BV2/Ron,sp),而随着SiC 衬底和外延质量的不断提升以及器件结构的持续优化,SiC 单极型器件的击穿电压与导通电阻之前的制约关系会逐渐接近一维理论极限(Ron,sp ∝ BV2.3~2.5)。由于比导通电阻与击穿电压的2.3 次方成正比,当击穿电压增加时,比导通电阻会急剧增加,导致SiC 单极型器件在中高压领域相比于Si 双极型器件(IGBT 等)的低导通损耗性能优势逐渐消失。因此,如何打破一维理论极限的桎梏、进一步降低器件的导通电阻成为SiC 功率器件未来研究的热点。

在硅基功率器件研究中,超结(Super junction)技术成功突破了单极型器件的一维理论极限,解决了单极型器件的击穿电压/ 导通电阻的制约问题,降低了器件的导通损耗, 并且实现了成熟的产业化应用。因此,在SiC 器件中应用超结技术有望显著提升单极型器件的导通性能,在中高压领域保持优势。然而,由于SiC 中p 型注入深度有限且掺杂元素难以扩散,传统硅基超结器件的制备方法很难适用,目前SiC 超结器件主要有四种技术方案,但都存在明显缺陷:1. 刻蚀深沟槽后使用外延生长来填充沟槽[4] :外延生长填槽工艺复杂,且在填槽过程中极易出现空洞,造成严重的器件可靠性问题;2. 多次外延生长,每次外延后进行离子注入[5] :工艺难度与工艺成本巨大,例如制备30 um 漂移区需要30+ 次外延,且每次外延时需要进行二次外延后的对准;3. 刻蚀深沟槽后进行侧壁离子注入,再用电介质填充沟槽[6] :受制于刻蚀的深宽比,沟槽面积会降低器件电流导通的有效面积, 造成导通电阻的提高。4. 采用多次外延和离子注入形成悬浮结,再通过超高能离子注入将悬浮结接地[7] :超高能离子注入机是通过改装粒子加速器来实现的,此方案无法推广,并且实现这种深度的p 型掺杂,对于SiC 晶格也有着无法修复的损伤,无法保证器件的可靠性。

综上所述,现有技术制备工艺难度大、制备成本高昂, 且器件可靠性问题严重,业界需要有可靠性、有可制造性、有规模量产价值的SiC 超结器件方案。九峰山实验室设计了基于多级沟槽的SiC 超结方案,为业界进一步降低SiC 功率器件的导通电阻提供了可行的解决方案。

如图8所示,为九峰山实验室的多级沟槽半超结MOSFET 器件。设计了多级台阶的SiC沟槽MOSFET 结构,通过离子注入的方式在栅极沟槽的下方形成与漂移区掺杂类型相反的电荷平衡区,在器件反向承压时,n型区域与p型区域在横向上相互耗尽,使电荷平衡区的电场强度保持一致,在不额外占用元胞面积的同时实现超结效果,提高器件的耐压值。同时在空间上将多级沟槽周围的电荷平衡区周期性接地, 避免p 型电荷平衡区的浮空,使得器件在由阻断状态转换为导通状态时,电荷平衡区有充足的少子进行补充,减小器件的开启时间,并且降低器件的开关损耗。为了实现电荷平衡, n 型电荷平衡区的掺杂浓度nx≥n-drift,n 型电荷平衡区在器件导通时具有电流扩展的能力,这使得器件在正向导通时可以实现更小的导通电阻。仿真结果表明,该多级沟槽MOSFET 的击穿电压可以达到1810V,比导通电阻为2.52mΩ/cm2, 大大降低了1800V SiC MOSFET 器件的导通电阻。

图8:SiC多级沟槽半超结器件结构示意图。

如图9 所示,为九峰山实验室的多级沟槽悬浮结器件。悬浮结器件(浮空结器件)通过在漂移区中设计不与电极直接连接,掺杂类型与漂移区相反的悬浮结区域,对漂移区的电场产生调制作用,使得器件可以在保持击穿电压不下降的情况下,提高漂移区的掺杂浓度来降低器件的导通电阻;或者在保持导通电阻不增加的情况下,提升器件的击穿电压。当器件阻断时(反向承压),悬浮结处于耗尽状态,当器件由阻断状态转换为导通状态时,悬浮结需要补充空穴来恢复到初始状态,但由于悬浮结并未与电极连接,只能通过漂移区的少子(空穴)来进行补充,因此造成器件有较大的开启延迟,这也使得器件开关的能量损耗较大。本方案不改变器件原本的结构(即所有具有漂移区的垂直器件均可采用此方案在漂移区中构建悬浮结并接地),通过刻蚀形成多级台阶的沟槽结构,再通过离子注入的方式形成P 型连接区,将每一层悬浮结接地,避免了高能P 离子注入,减小对材料的损伤,并且使得器件在由阻断状态转换为导通状态时,悬浮结有充足的少子(空穴或电子)进行补充,减小器件的开启时间, 并且降低器件的导通损耗。多级沟槽与单级沟槽相比,在沟槽深度相同、离子注入条件相同的情况下,多级沟槽形成的掺杂区域可以很好的包裹住沟槽,使得所有悬浮结都可以很好的接地,同时也避免了沟槽的漏电风险。

图9:SiC多级沟槽悬浮结器件结构示意图。

总结与展望

SiC 由于其更优异的材料性能在电力电子领域的需求迅速升温,并在新能源汽车、光伏、轨道交通、智能电网等产业中得到了广泛的应用。随着SiC 衬底、外延质量以及相关特殊工艺能力的提升,SiC 器件结构设计成为了当下研究的热点,而沟槽结构因其独特的优势成为二极管与MOSFET 器件的主流设计。国外对于SiC 沟槽器件的研究较早,以Rohm 和Infineon 为代表的龙头企业已有沟槽结构的产品上市,并逐步建立专利壁垒、占据多数市场,而国内在SiC 沟槽器件的研究上处于起步阶段,需要尽快建立SiC 沟槽器件IP 体系,培养结构设计与全套工艺的能力。

扩展阅读

[1] F. Bjoerk, J. Hancock, M. Treu, et al. 2nd generation 600V SiC Schottky diodes use merged pn/Schottky structure for surge overload protection. in: Twenty-First Annual IEEE Applied Power Electronics Conference and Exposition, Proceedings of the IEEE, 2006

[2] M.Aketaa, Y.Yokotsuji, M.Miura, et al. 4H-SiC Trench Structure Schottky Diodes, Materials Science Forum Vols, 2012, 717-720: 933-936

[3] J.Yuan, J.Li, K.Xiao, First Experimental Demonstration of 4H-SiC Multi-Step Trenched Junction Barrier Schottky Diode Developed at JFS Lab. in: The 4th International Conference on Power and Energy Technology, Proceedings of the IEEE, 2022

[4] R.Kosugi, S.Ji, K.Mochizukiin, et al. Breaking the Theoretical Limit of 6.5 kV-Class 4H-SiC Super-Junction (SJ) MOSFETs by Trench-Filling Epitaxial Growth. in: Proceedings of the 31st International Symposium on Power Semiconductor Devices & ICs, Proceedings of the IEEE, 2019

[5] S.Harada, Y.Kobayashi, S.Kyogoku, et al. First Demonstration of Dynamic characteristics for SiC Superjunction MOSFET Realized using Multi-epitaxial Growth Method. in: IEEE International Electron Devices Meeting (IEDM), Proceedings of the IEEE, 2018

[6] H.Wang, C.Wang, B.Wang, et al. 4H-SiC Super-Junction JFET: Design and Experimental Demonstration. IEEE Electron Device Letters, 2020, VOL. 41, NO. 3,

[7] R. Ghandi, C. Hitchcock, S. Kennerly, et al. Scalable Ultrahigh Voltage SiC Superjunction Device Technologies for Power Electronics Applications. in: IEEE International Electron Devices Meeting (IEDM), Proceedings of the IEEE, 2022.

扫一扫,在手机端打开当前页

- 上一篇:碳化硅同质外延层厚度无损红外反射光谱法分析

- 下一篇: 硅基化合物异质集成技术